# 26V, 1.2MHz Rail-to-Rail Output CMOS Operational Amplifier

#### 1 FEATURES

- Qualified for Automotive Applications

- AEC-Q100 Qualified with the Grade 1

- HIGH GAIN BANDWIDTH: 1.2MHz

- INPUT OFFSET VOLTAGE: ±0.5mV (Typical)

- QUIESCENT CURRENT: 120uA/Amp

- Rail to Rail Output

- Common-Mode Input Voltage Range Include Ground

- Supply Range: +3V to +26V

- SPECIFIED UP TO +125°C

- Micro SIZE PACKAGES: TSSOP14

#### **2 APPLICATIONS**

- SENSORS

- PHOTODIODE AMPLIFICATION

- ACTIVE FILTERS

- TEST EQUIPMENT

- DRIVING A/D CONVERTERS

#### 3 DESCRIPTIONS

The RS8414-Q1 families of products offer high voltage (26V) operation and rail-to-rail output, as well as excellent speed/power consumption ratio, providing an excellent bandwidth (1.2MHz) and slew rate of 0.67V/us. The op-amps are unity gain stable and feature an ultra-low input bias current.

The devices are stable at capacitance up to 300pF. The input can operate normally within 100mV below of the negative power rail to 2V below of the positive power rail. The RS8414-Q1 families of operational amplifiers are specified at the full temperature range of -40°C to +125°C under single power supplies of 3V to 26V or dual power supplies of  $\pm 1.5$ V to  $\pm 13$ V.

#### Device Information (1)

| PART NUMBER | PACKAGE | BODY SIZE(NOM) |  |  |

|-------------|---------|----------------|--|--|

| RS8414-Q1   | TSSOP14 | 5.00mm×4.40mm  |  |  |

<sup>(1)</sup> For all available packages, see the orderable addendum at the end of the data sheet.

## **Table of Contents**

| 1 FEATURES                                   |    |

|----------------------------------------------|----|

| 2 APPLICATIONS                               |    |

| 3 DESCRIPTIONS                               |    |

| 4 REVISION HISTORY                           | 3  |

| 5 PACKAGE/ORDERING INFORMATION (1)           | 4  |

| 6 PIN CONFIGURATION AND FUNCTIONS (TOP VIEW) | 5  |

| 7 SPECIFICATIONS                             | 6  |

| 7.1 Absolute Maximum Ratings                 | 6  |

| 7.2 ESD Ratings                              | 6  |

| 7.3 Recommended Operating Conditions         | 6  |

| 7.4 ELECTRICAL CHARACTERISTICS               | 7  |

| 7.5 TYPICAL CHARACTERISTICS                  | 9  |

| 8 DETAILED DESCRIPTION                       | 11 |

| 8.1 Overview                                 | 11 |

| 8.2 Operating Characteristics                | 11 |

| 8.3 Electrical Overstress                    | 11 |

| 9 APPLICATION AND IMPLEMENTATION             | 13 |

| 9.1 APPLICATION NOTE                         | 13 |

| 9.2 Typical Applications                     | 13 |

| 9.3 Design Requirements                      | 13 |

| 9.4 Detailed Design Procedure                | 13 |

| 10 LAYOUT                                    | 14 |

| 10.1 Layout Guidelines                       | 14 |

| 10.2 Layout Example                          | 14 |

| 11 PACKAGE OUTLINE DIMENSIONS                | 15 |

| 12 TAPE AND REEL INFORMATION                 | 16 |

## **4 REVISION HISTORY**

Note: Page numbers for previous revisions may different from page numbers in the current version.

| Version        | Change Date | Change Item               |

|----------------|-------------|---------------------------|

| A.1            | 2024/01/24  | Initial version completed |

| A.1.1          | 2024/03/07  | Modify packaging naming   |

| A.2 2025/02/27 |             | Delete SOP14 Package      |

## 5 PACKAGE/ORDERING INFORMATION (1)

| Orderable<br>Device | Package<br>Type | Pin | Channel | Lead<br>finish/Ball<br>material <sup>(2)</sup> | MSL Peak<br>Temp <sup>(3)</sup> | Op Temp(°C)  | Device<br>Marking | Package<br>Qty        |

|---------------------|-----------------|-----|---------|------------------------------------------------|---------------------------------|--------------|-------------------|-----------------------|

| RS8414XP<br>-Q1     | TSSOP14         | 14  | 4       | NIPDAUAG                                       | MSL1-260°-<br>Unlimited         | -40°C ~125°C | RS8414            | Tape and<br>Reel,4000 |

- (1) This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the right-hand navigation.

- (2) Lead finish/Ball material. Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

- (3) RUNIC classify the MSL level with using the common preconditioning setting in our assembly factory conforming to the JEDEC industrial standard J-STD-20F, Please align with RUNIC if your end application is quite critical to the preconditioning setting or if you have special requirement.

- (4) There may be additional marking, which relates to the lot trace code information (data code and vendor code), the logo or the environmental category on the device.

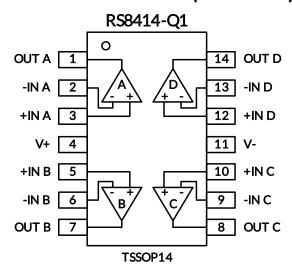

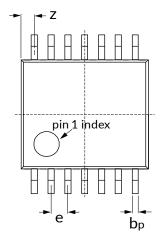

## **6 PIN CONFIGURATION AND FUNCTIONS (TOP VIEW)**

## **Pin Description**

| NAME | PIN     | 1.(0.(1) | DESCRIPTION                                                            |  |  |  |  |

|------|---------|----------|------------------------------------------------------------------------|--|--|--|--|

| NAME | TSSOP14 | I/O (1)  | DESCRIPTION                                                            |  |  |  |  |

| -INA | 2       | - 1      | Inverting input, channel A                                             |  |  |  |  |

| +INA | 3       | 1        | Noninverting input, channel A                                          |  |  |  |  |

| -INB | 6       | 1        | Inverting input, channel B                                             |  |  |  |  |

| +INB | 5       | - 1      | Noninverting input, channel B                                          |  |  |  |  |

| -INC | 9       | - 1      | Inverting input, channel C                                             |  |  |  |  |

| +INC | 10      | - 1      | Noninverting input, channel C                                          |  |  |  |  |

| -IND | 13      | 1        | Inverting input, channel D                                             |  |  |  |  |

| +IND | 12      | I        | Noninverting input, channel D                                          |  |  |  |  |

| OUTA | 1       | 0        | Output, channel A                                                      |  |  |  |  |

| OUTB | 7       | 0        | Output, channel B                                                      |  |  |  |  |

| OUTC | 8       | 0        | Output, channel C                                                      |  |  |  |  |

| OUTD | 14      | 0        | Output, channel D                                                      |  |  |  |  |

| V-   | 11      | -        | Negative (lowest) power supply or ground (for single supply operation) |  |  |  |  |

| V+   | 4       | -        | Positive (highest) power supply                                        |  |  |  |  |

<sup>(1)</sup> I = Input, O = Output.

### **7 SPECIFICATIONS**

#### 7.1 Absolute Maximum Ratings

Over operating free-air temperature range (unless otherwise noted) (1)

|             | · · · · · · ·                           |          | MIN       | MAX        | UNIT |  |

|-------------|-----------------------------------------|----------|-----------|------------|------|--|

|             | Supply, Vs=(V+) - (V-)                  | -0.7     | 26        |            |      |  |

| Voltage     | Signal input pin <sup>(2)</sup>         | (V-)-0.2 | (V+) +0.2 | V          |      |  |

|             | Signal output pin <sup>(3)</sup>        |          | (V-)-0.2  | (V+) +0.2  |      |  |

|             | Signal input pin <sup>(2)</sup>         | -10      | 10        | mA         |      |  |

| Current     | Signal output pin <sup>(3)</sup>        |          | -100      | 100        | mA   |  |

|             | Output short-circuits (4)               |          | Conti     | Continuous |      |  |

| θJA         | Package thermal impedance (5)           | TSSOP14  |           | 90         | °C/W |  |

|             | Operating range, T <sub>A</sub>         | -40      | 125       |            |      |  |

| Temperature | Junction, T <sub>J</sub> <sup>(6)</sup> | -40      | 150       | °C         |      |  |

|             | Storage, T <sub>stg</sub>               |          | -55       | 150        |      |  |

<sup>(1)</sup> Stresses above these ratings may cause permanent damage. Exposure to absolute maximum conditions for extended periods may degrade device reliability. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those specified is not implied.

- (4) Short-circuit to ground, one amplifier per package.

- (5) The package thermal impedance is calculated in accordance with JESD-51.

- (6) The maximum power dissipation is a function of  $T_{J(MAX)}$ ,  $R_{\theta JA}$ , and  $T_A$ . The maximum allowable power dissipation at any ambient temperature is  $P_D = (T_{J(MAX)} T_A) / R_{\theta JA}$ . All numbers apply for packages soldered directly onto a PCB.

#### 7.2 ESD Ratings

The following ESD information is provided for handling of ESD-sensitive devices in an ESD protected area only.

|                                            |                                              |                                              | VALUE | UNIT |

|--------------------------------------------|----------------------------------------------|----------------------------------------------|-------|------|

| V <sub>(ESD)</sub> Electrostatic discharge | Human-Body Model (HBM), per AEC Q100-002 (1) | ±2000                                        | \/    |      |

|                                            | Electrostatic discharge                      | Charged-Device Model (CDM), per AEC Q100-011 | ±500  | V    |

|                                            |                                              | Latch-Up (LU), per AEC Q100-004              | ±100  | mA   |

(1) AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

#### **ESD SENSITIVITY CAUTION**

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### 7.3 Recommended Operating Conditions

Over operating free-air temperature range (unless otherwise noted).

|                                              |               | MIN  | NOM | MAX | UNIT |

|----------------------------------------------|---------------|------|-----|-----|------|

| Supply valtage \(\( \) \( \) \( \)           | Single-supply | 3    |     | 26  | \/   |

| Supply voltage, V <sub>S</sub> = (V+) - (V-) | Dual-supply   | 1101 | V   |     |      |

| Operating range, T <sub>A</sub>              |               | -40  |     | 125 | °C   |

<sup>(2)</sup> Input terminals are diode-clamped to the power-supply rails. Input signals that can swing more than 0.2V beyond the supply rails should be current-limited to 10mA or less.

<sup>(3)</sup> Output terminals are diode-clamped to the power-supply rails. Output signals that can swing more than 0.2V beyond the supply rails should be current-limited to ±100mA or less.

## 7.4 ELECTRICAL CHARACTERISTICS

(At  $T_A$  = +25°C,  $V_S$ =3V to 26V,  $R_L$  = 10k $\Omega$  connected to  $V_S/2$ , and  $V_{OUT}$  =  $V_S/2$ , Full  $^{(9)}$  = -40°C to +125°C, unless otherwise noted.)  $^{(1)}$

|                 | DADAMITTED                                           | CONDITIONS                                                     | -    | R                  |                |                    |          |  |

|-----------------|------------------------------------------------------|----------------------------------------------------------------|------|--------------------|----------------|--------------------|----------|--|

|                 | PARAMETER                                            | CONDITIONS                                                     | T,   | MIN <sup>(2)</sup> | <b>TYP</b> (3) | MAX <sup>(2)</sup> | UNIT     |  |

| POWER           | SUPPLY                                               |                                                                |      |                    | •              |                    |          |  |

| Vs              | Operating Voltage Range                              |                                                                | 25°C | 3                  |                | 26                 | V        |  |

|                 |                                                      | \\ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \                         | 25°C |                    | 120            | 230                |          |  |

| ,               | Quiescent Current Per                                | V <sub>S</sub> =±2.5V, Io=0mA                                  | Full |                    |                | 270                |          |  |

| Ιq              | Amplifier                                            | \/ \  \  \  \  \  \  \  \  \  \  \  \  \                       | 25°C |                    | 150            | 300                | μΑ       |  |

|                 |                                                      | V <sub>S</sub> =±13V, Io=0mA                                   | Full |                    |                | 350                |          |  |

| DCDD            | Dower Cumply Dejection Detic                         | \/E\/+0.24\/                                                   | 25°C | 95                 | 120            |                    | dB       |  |

| PSRR            | Power-Supply Rejection Ratio                         | V <sub>S</sub> =5V to 26V                                      | Full | 90                 |                |                    | aB       |  |

| NPUT            |                                                      |                                                                |      |                    |                |                    |          |  |

| Voc             | Input Offset Voltage                                 | V <sub>CM</sub> = V <sub>S</sub> /2                            | 25°C | -2                 | ±0.5           | 2                  | mV       |  |

| Vos             | Input Offset Voltage                                 | VCM= VS/Z                                                      | Full | -3                 |                | 3                  | mv       |  |

| Vos Tc          | Input Offset Voltage Average<br>Drift <sup>(4)</sup> |                                                                | Full |                    | ±3             |                    | μV/°     |  |

| IB              | Input Bias Current (4) (5)                           | V <sub>CM</sub> = V <sub>S</sub> /2                            | 25°C |                    | ±10            |                    | pА       |  |

| los             | Input Offset Current (4)                             | V <sub>CM</sub> = V <sub>S</sub> /2                            | 25°C |                    | ±10            |                    | pА       |  |

| V <sub>СМ</sub> | Common-Mode Voltage<br>Range                         | V <sub>S</sub> = ±13V                                          | Full | (V-)-0.1           |                | (V+)-2             | V        |  |

| CNADD           | Common-Mode Rejection                                | V <sub>S</sub> = ±13V                                          | 25°C | 100                | 110            |                    | -        |  |

| CMRR            | Ratio                                                | V <sub>CM</sub> =(V-)+0.5V to (V+)-2V                          | Full | 90                 |                |                    | dB       |  |

| OUTPU           | Т                                                    |                                                                |      |                    |                |                    |          |  |

| Λ               | Open Leen Veltage Cain                               | R <sub>L</sub> =10KΩ, Vo=(V-)+0.6V                             | 25°C | 83                 | 115            |                    | dB       |  |

| A <sub>OL</sub> | Open-Loop Voltage Gain                               | to (V+)-0.6V                                                   | Full | 53                 |                |                    | иь       |  |

| \/ - · ·        |                                                      |                                                                | 25°C | 12.8               |                |                    | <b>V</b> |  |

| Vон             | Output Swing                                         | V <sub>S</sub> =±13V, R <sub>L</sub> =10KΩ                     | Full | 12.7               |                |                    | ]        |  |

| $V_{OL}$        | Output Swing                                         | VS-±13V, KL-10K22                                              | 25°C |                    |                | -12.8              | \/       |  |

| VOL             |                                                      |                                                                | Full |                    |                | -12.7              | V        |  |

| L               | Short-Circuit Current (6) (7)                        |                                                                | 25°C | ±34                | ±80            |                    | Л        |  |

| Isc             | Short-Circuit Current                                |                                                                | Full | ±15                |                |                    | mA       |  |

| CLOAD           | Capacitive Load Drive                                |                                                                | 25°C |                    | 100            |                    | pF       |  |

| FREQUE          | ENCY RESPONSE                                        |                                                                |      |                    |                |                    |          |  |

| SR              | Slew Rate <sup>(8)</sup>                             | G=+1, C <sub>L</sub> =100pF                                    | 25°C |                    | 0.67           |                    | V/µ      |  |

| GBW             | Gain-Bandwidth Product                               |                                                                | 25°C |                    | 1.2            |                    | MH       |  |

| ts              | Settling Time,0.1%                                   | V <sub>S</sub> =±2.5V, G=+1,<br>C <sub>L</sub> =100pF, Step=2V | 25°C |                    | 5              |                    | μs       |  |

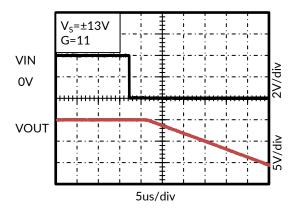

| $t_{OR}$        | Overload Recovery Time                               | V <sub>IN</sub> •Gain≥V <sub>S</sub> , G=11                    | 25°C |                    | 5              |                    | μs       |  |

| ton             | Turn On Time                                         |                                                                | 25°C |                    | 10             |                    | μs       |  |

| NOISE           |                                                      |                                                                |      |                    |                |                    |          |  |

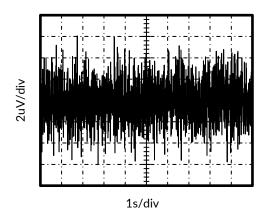

| En              | Input Voltage Noise                                  | f = 0.1Hz to 10Hz,<br>V <sub>S</sub> =±2.5V                    | 25°C |                    | 16             |                    | μVp      |  |

| en              | Input Voltage Noise Density (4)                      | f = 1KHz                                                       | 25°C |                    | 45             |                    | nV/√     |  |

- (1) Electrical table values apply only for factory testing conditions at the temperature indicated. Factory testing conditions result in very limited self-heating of the device.

- (2) Limits are 100% production tested at 25°C. Limits over the operating temperature range are ensured through correlations using statistical quality control (SQC) method.

- (3) Typical values represent the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration.

- (4) This parameter is ensured by design and/or characterization and is not tested in production.

- (5) Positive current corresponds to current flowing into the device.

- (6) The maximum power dissipation is a function of  $T_{J(MAX)}$ ,  $R_{\theta JA}$ , and  $T_A$ . The maximum allowable power dissipation at any ambient temperature is PD =  $(T_{J(MAX)} T_A) / R_{\theta JA}$ . All numbers apply for packages soldered directly onto a PCB.

- (7) Short circuit test is a momentary test.

- (8) Number specified is the slower of positive and negative slew rates.

- (9) Specified by characterization only.

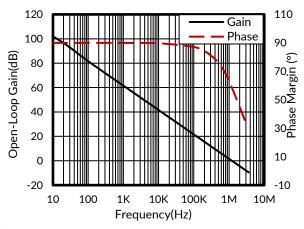

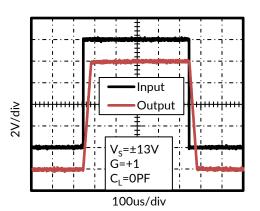

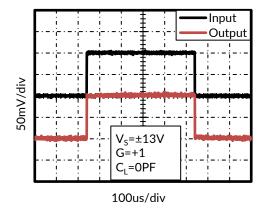

#### 7.5 TYPICAL CHARACTERISTICS

NOTE: The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only.

At  $T_A$  = +25°C,  $V_S$ =±13 $V_S$ ,  $R_L$  = 10 $k\Omega$  connected to  $V_S$ /2,  $V_{OUT}$  =  $V_S$ /2, unless otherwise noted.

Figure 1. OPEN-LOOP GAIN AND PHASE vs FREQUENCY

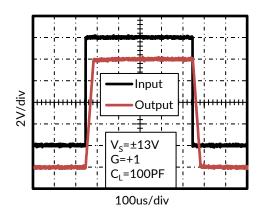

Figure 3. LARGE SIGNAL STEP RESPONSE

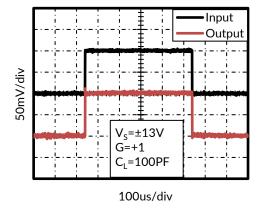

Figure 5. SMALL SIGNAL STEP RESPONSE

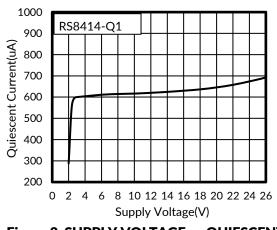

Figure 2. SUPPLY VOLTAGE vs QUIESCENT CURRENT

Figure 4. LARGE SIGNAL STEP RESPONSE

Figure 6. SMALL SIGNAL STEP RESPONSE

9 / 17 www.run-ic.com

#### TYPICAL CHARACTERISTICS

NOTE: The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only.

At  $T_A = +25$ °C,  $V_S = \pm 13V$ ,  $R_L = 10k\Omega$  connected to  $V_S/2$ ,  $V_{OUT} = V_S/2$ , unless otherwise noted.

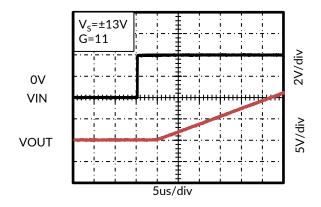

Figure 7. POSITIVE OVERVOLTAGE RECOVERY

Figure 8. NEGATIVE OVERVOLTAGE RECOVERY

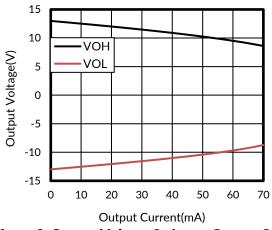

Figure 9. Output Voltage Swing vs Output Current

Figure 10. 0.1Hz to 10Hz NOISE AT Vs=5V

#### 8 DETAILED DESCRIPTION

#### 8.1 Overview

The RS8414-Q1 operational amplifier provides high overall performance, making these devices designed for many general-purpose applications. The excellent offset drift of only  $3\mu V/^{\circ}C$  provides excellent stability over the entire temperature range. In addition, the device offers very good overall performance with high CMRR, PSRR, and AoL.

#### 8.2 Operating Characteristics

The RS8414-Q1 amplifier is specified for operation from 3 V to 26 V ( $\pm 1.5$  V to  $\pm 13$  V). Many of the specifications apply from -40°C to +125°C.

#### 8.3 Electrical Overstress

Designers often ask questions about the capability of an operational amplifier to withstand electrical overstress. These questions tend to focus on the device inputs, but can involve the supply voltage pins or even the output pin. Each of these different pin functions have electrical stress limits determined by the voltage breakdown characteristics of the particular semiconductor fabrication process and specific circuits connected to the pin. Additionally, internal electrostatic discharge (ESD) protection is built into these circuits for protection from accidental ESD events both before and during product assembly.

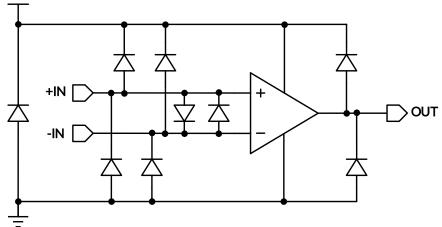

A good understanding of this basic ESD circuitry and the relevance to an electrical overstress event is helpful. Figure 11 shows the ESD circuits contained in the RS8414-Q1. The ESD protection circuitry involves several current-steering diodes connected from the input and output pins and routed back to the internal power-supply lines, where the diodes meet at an absorption device internal to the operational amplifier. This protection circuitry is intended to remain inactive during normal circuit operation.

Figure 11. ESD block diagram

An ESD event produces a short-duration, high-voltage pulse that is transformed into a short-duration, high current pulse when discharging through a semiconductor device. The ESD protection circuits are designed to provide a current path around the operational amplifier core to prevent damage. The energy absorbed by the protection circuitry is then dissipated as heat.

When an ESD voltage develops across two or more amplifier device pins, current flows through one or more steering diodes. Depending on the path that the current takes, the absorption device can activate. The absorption device has a trigger, or threshold voltage, that is above the normal operating voltage of the RS8414-Q1 but below the device breakdown voltage level. When this threshold is exceeded, the absorption device quickly activates and clamps the voltage across the supply rails to a safe level.

When the operational amplifier connects into a circuit, as shown in Figure 11, the ESD protection components are intended to remain inactive and do not become involved in the application circuit operation. However, circumstances can arise where an applied voltage exceeds the operating voltage range of a given pin. If this condition occurs, there is a risk that some internal ESD protection circuits can turn on and conduct current. Any such current flow occurs through steering-diode paths and rarely involves the absorption device.

Much of what happens in the circuit depends on the supply characteristics. If V+ can sink the current, then one of the upper input steering diodes conducts and directs current to V+. Excessively high current levels can flow with increasingly higher  $V_{IN}$ . As a result, the data sheet specifications recommend that applications limit the input current to 10 mA.

If the supply is not capable of sinking the current,  $V_{IN}$  can begin sourcing current to the operational amplifier and then take over as the source of positive supply voltage. The danger in this case is that the voltage can rise to levels that exceed the operational amplifier absolute maximum ratings.

Another common question involves what happens to the amplifier if an input signal is applied to the input when the power supplies (V+ or V-) are at 0 V. Again, this question depends on the supply characteristic when at 0 V, or at a level below the input signal amplitude. If the supplies appear as high impedance, then the input source supplies the operational amplifier current through the current-steering diodes. This state is not a normal bias condition; most likely, the amplifier does not operate normally. If the supplies are low impedance, then the current through the steering diodes can become quite high. The current level depends on the ability of the input source to deliver current and any resistance in the input path.

The input pins of the RS8414-Q1 are protected from excessive differential voltage with back-to-back diodes; see Figure 11. In most circuit applications, the input protection circuitry has no effect. However, in low-gain or G = 1 circuits, fast-ramping input signals can forward-bias these diodes because the output of the amplifier cannot respond rapidly enough to the input ramp. If the input signal is fast enough to create this forward-bias condition, then limit the input signal current to 10 mA or less. If the input signal current is not inherently limited, an input series resistor can limit the input signal current. This input series resistor degrades the low-noise performance of the RS8414-Q1. Figure 11 shows an example configuration that implements a current-limiting feedback resistor.

#### 9 APPLICATION AND IMPLEMENTATION

Information in the following applications sections is not part of the RUNIC component specification, and RUNIC does not warrant its accuracy or completeness. RUNIC's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

#### 9.1 APPLICATION NOTE

The RS8414-Q1 operational amplifier provides high overall performance in a large number of general-purpose applications. As with all amplifiers, applications with noisy or high-impedance power supplies require decoupling capacitors placed close to the device pins. In most cases,  $0.1\mu F$  capacitors are adequate. Follow the additional recommendations in the Layout Guidelines section to achieve the maximum performance from this device. Many applications introduce capacitive loading to the output of the amplifier (which potentially causes instability). To stabilize the amplifier, add an isolation resistor between the amplifier output and the capacitive load.

#### 9.2 Typical Applications

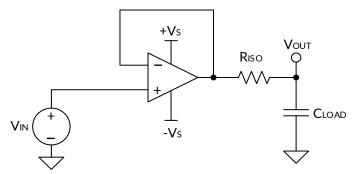

This circuit can drive capacitive loads (such as cable shields, reference buffers, MOSFET gates, and diodes). The circuit uses an isolation resistor ( $R_{\rm ISO}$ ) to stabilize the output of an operational amplifier.  $R_{\rm ISO}$  modifies the open-loop gain of the system to ensure that the circuit has sufficient phase margin.

Figure 12. Unity-Gain Buffer with R<sub>ISO</sub> Stability Compensation

#### 9.3 Design Requirements

The design requirements are:

• Supply voltage: 30 V (±15 V)

• Capacitive loads: 100 pF, 1000 pF, 0.01μF, 0.1μF, and 1μF

Phase margin: 45° and 60°

#### 9.4 Detailed Design Procedure

Figure 12 shows a unity-gain buffer driving a capacitive load. Equation 1 shows the transfer function for the circuit in Figure 12. Figure 12 does not show the open-loop output resistance of the operational amplifier (R<sub>o</sub>).

$$T(s) = \frac{1 + C_{LOAD} \times R_{ISO} \times S}{1 + (R_0 + R_{ISO}) \times C_{LOAD} \times S}$$

(1)

The transfer function in Equation 1 has a pole and a zero. The frequency of the pole ( $f_p$ ) is determined by (Ro +R<sub>ISO</sub>) and C<sub>LOAD</sub>. The R<sub>ISO</sub> and C<sub>LOAD</sub> components determine the frequency of the zero ( $f_z$ ). A stable system is obtained by selecting R<sub>ISO</sub> so that the rate of closure (ROC) between the open-loop gain (A<sub>OL</sub>) and 1/ $\beta$  is 20 dB per decade.

13 / 17 www.run-ic.com

#### **10 LAYOUT**

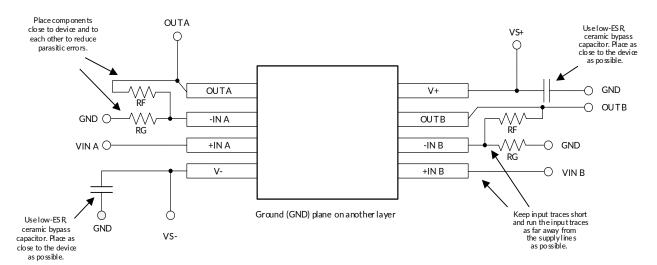

#### 10.1 Layout Guidelines

For best operational performance of the device, use good printed circuit board (PCB) layout practices, including:

- Noise can propagate into analog circuitry through the power pins of the circuit as a whole and the operational amplifier itself. Bypass capacitors are used to reduce the coupled noise by providing low impedance power sources local to the analog circuitry.

- —Connect low-ESR,  $0.1\mu F$  ceramic bypass capacitors between each supply pin and ground, placed as close to the device as possible. A single bypass capacitor from V+ to ground is applicable for single supply applications.

- Separate grounding for analog and digital portions of the circuitry is one of the simplest and most effective

methods of noise suppression. One or more layers on multilayer PCBs are usually devoted to ground planes.

A ground plane helps distribute heat and reduces electromagnetic interference (EMI) noise pickup. Make

sure to physically separate digital and analog grounds, paying attention to the flow of the ground current.

- In order to reduce parasitic coupling, run the input traces as far away from the supply or output traces as possible. If these traces cannot be kept separate, crossing the sensitive trace perpendicularly is much better than in parallel with the noisy trace.

- Place the external components as close to the device as possible. As shown in Figure 14, keeping R<sub>F</sub> and R<sub>G</sub> close to the inverting input minimizes parasitic capacitance.

- Keep the length of input traces as short as possible. Always remember that the input traces are the most sensitive part of the circuit.

- Consider a driven, low-impedance guard ring around the critical traces. A guard ring can significantly reduce leakage currents from nearby traces that are at different potentials.

#### 10.2 Layout Example

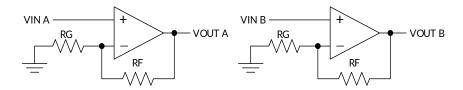

Figure 13. Schematic Representation

Figure 14. Layout Example

NOTE: Layout Recommendations have been shown for dual op-amp only, follow similar precautions for Single and four.

14 / 17 www.run-ic.com

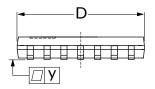

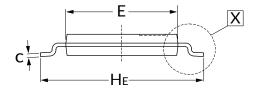

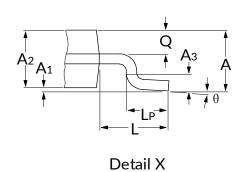

## 11 PACKAGE OUTLINE DIMENSIONS TSSOP14 (2)

RECOMMENDED LAND PATTERN (Unit: mm)

| Complete         | Dimensions I | n Millimeters | Dimension | s In Inches |

|------------------|--------------|---------------|-----------|-------------|

| Symbol           | Min          | Max           | Min       | Max         |

| A <sup>(1)</sup> |              | 1.100         |           | 0.043       |

| A <sub>1</sub>   | 0.050        | 0.150         | 0.002     | 0.006       |

| A <sub>2</sub>   | 0.800        | 0.950         | 0.031     | 0.037       |

| A <sub>3</sub>   | 0.2          | 250           | 0.0       | 010         |

| bp               | 0.190        | 0.300         | 0.007     | 0.012       |

| С                | 0.100        | 0.200         | 0.004     | 0.008       |

| D <sup>(1)</sup> | 4.900        | 5.100         | 0.193     | 0.201       |

| E <sup>(1)</sup> | 4.300        | 4.500         | 0.169     | 0.177       |

| HE               | 6.200        | 6.600         | 0.244     | 0.260       |

| е                | 0.6          | 550           | 0.0       | 026         |

| L                | 1.0          | 000           | 0.0       | )39         |

| Lp               | 0.500        | 0.750         | 0.020     | 0.030       |

| Q                | 0.300        | 0.400         | 0.012     | 0.016       |

| Z                | 0.380        | 0.720         | 0.015     | 0.028       |

| У                | 0.1          | .00           | 0.0       | 004         |

| θ                | 0°           | 8°            | 0°        | 8°          |

- 1. Plastic or metal protrusions of 0.15mm maximum per side are not included.

- 2. This drawing is subject to change without notice.

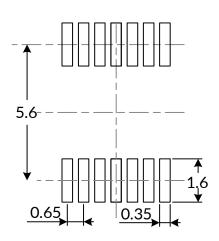

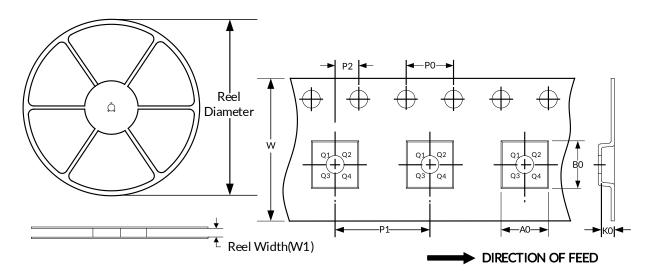

## 12 TAPE AND REEL INFORMATION REEL DIMENSIONS

#### **TAPE DIMENSION**

NOTE: The picture is only for reference. Please make the object as the standard.

#### **KEY PARAMETER LIST OF TAPE AND REEL**

| Package Type | Reel<br>Diameter | Reel Width<br>W1(mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P0<br>(mm) | P1<br>(mm) | P2<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|------------------|----------------------|------------|------------|------------|------------|------------|------------|-----------|------------------|

| TSSOP14      | 13"              | 12.4                 | 6.95       | 5.60       | 1.20       | 4.0        | 8.0        | 2.0        | 12.0      | Q1               |

- 1. All dimensions are nominal.

- 2. Plastic or metal protrusions of 0.15mm maximum per side are not included.

#### IMPORTANT NOTICE AND DISCLAIMER

Jiangsu RUNIC Technology Co., Ltd. will accurately and reliably provide technical and reliability data (including data sheets), design resources (including reference designs), application or other design advice, WEB tools, safety information and other resources, without warranty of any defect, and will not make any express or implied warranty, including but not limited to the warranty of merchantability Implied warranty that it is suitable for a specific purpose or does not infringe the intellectual property rights of any third party.

These resources are intended for skilled developers designing with RUNIC products You will be solely responsible for: (1) Selecting the appropriate products for your application; (2) Designing, validating and testing your application; (3) Ensuring your application meets applicable standards and any other safety, security or other requirements; (4) RUNIC and the RUNIC logo are registered trademarks of RUNIC INCORPORATED. All trademarks are the property of their respective owners; (5) For change details, review the revision history included in any revised document. The resources are subject to change without notice. Our company will not be liable for the use of this product and the infringement of patents or third-party intellectual property rights due to its use.