运算放大器用作比较器的注意事项

2020-03-03

2020-03-03运算放大器和比较器

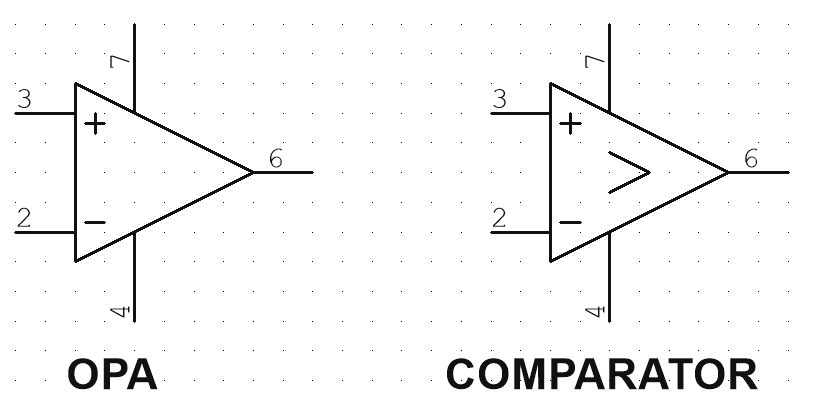

比较器和运算放大器电气符号非常相像,都是有反相、同相两个输入端和一个输出端的器件,输出端的输出电压范围一般在供电的轨到轨之间;同时比较器和运算放大器都具有低偏置电压、高增益和高共模抑制比的特点。

图1 运算放大器和比较器

运算放大器和比较器的区别

①输出:

比较器一般为逻辑输出,表征两个输入端的电位高低。现在市面上大部分比较器的输出都可以兼容TTL和CMOS,比较器的输出始终为正负电源轨之一。但是运算放大器的输出是模拟信号,目前CMOS型的运放输出一般都能做到轨到轨输出【1】,运放的输出电压信号可以是接近正负电源轨之间的任意值。在运算放大器输出动态范围不超过后端逻辑电路的供电轨条件下,运放是可以用作比较器的。

运放用作比较器时,输出是推挽架构;而比较器可以做成推挽架构,也可以做成开漏输出架构。

②速度

比较器适用于开环系统,高速条件下工作,通常比较稳定。运算放大器过驱时可能会饱和,使得恢复速度相对较慢,而比较器的过载恢复时间很短。

③输入考虑因素:

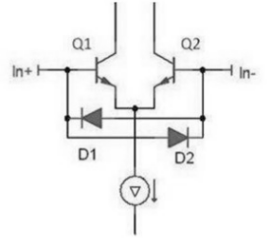

很多运算放大器都内置保护电路,以防止大电压损坏芯片。当输入较大差分电压时,很多运算放大器的输入级都会出现异常,因为运算放大器的差分输入电压范围通常是有限制的。

图2 运放内部输入保护电路

非轨对轨运放的共模输入电压范围,不能到正电源轨;而比较器是支持到正电源轨的。

运放用作比较器的应用场景

运放和比较器有很多相似的参数,在要求低失调电压、低失调电流、高共模抑制的应用场景中选择运放替代比较器是比较方便的。

运放一般有单运放,双运放和四运放的封装。将运放用作比较器,用一颗双运放或者四运放就可以完成信号放大加比较的功能。无论是在便捷性、成本还是电路板的体积上,都会更有优势。

运放用做比较器的缺点

从辩证的角度来看,有优点就一定会有缺点。在前文的区别中,我们已经提及到了运放和比较器的速度上的差异。因此在运放用作比较器时,需要重点关注速度、差分输入电压范围和放大器输出是否过载这几点。

运放作比较器的注意事项

①电源:

如果逻辑和运算放大器共用同一电源,轨到轨运算放大器可以驱动CMOS和TTL逻辑,但运算放大器与逻辑电路如果不共用电源,则需要另外做接口电路。

②输入阻抗和偏置电流:

运放用作比较器时,首先要满足高输入阻抗条件。CMOS运放这种电压反馈运算放大器的输入阻抗都在兆欧级别,满足应用。而对于电流反馈(跨导)运算放大器来说,反相输入端阻抗极低,不能用作比较器。

③差分输入特性

运算放大器的设计初衷是与负反馈配合,尽可能地降低差分输入。在具体的应用中应结合实际需要的差分输入电压、与运放实际能提供的最大差分输入电压来考虑。

④共模输入特性

对于老式的FET型输入运算放大器,当输入超过器件允许的共模电压范围时,会产生相位翻转。目前各个厂家生产的运放都通过各种手段尽量不让运放出现相位翻转的现象。如果实际的共模电压范围超过运放允许的输入共模电压范围,需要实际验证确认是否正常工作。

⑤稳定性

用作比较器的运放由于外部没有负反馈,开环增益非常高,因此,诸如PCB的寄生电容,同相输入端的对地阻抗都可能会引起放大器的输出震荡,在设计上要重点考虑。

备注:

【1】CMOS 架构的运放在低电流输出时,饱和压降非常小,甚至只有几mV,输出可以非常接近两个电源轨,而不是等于。

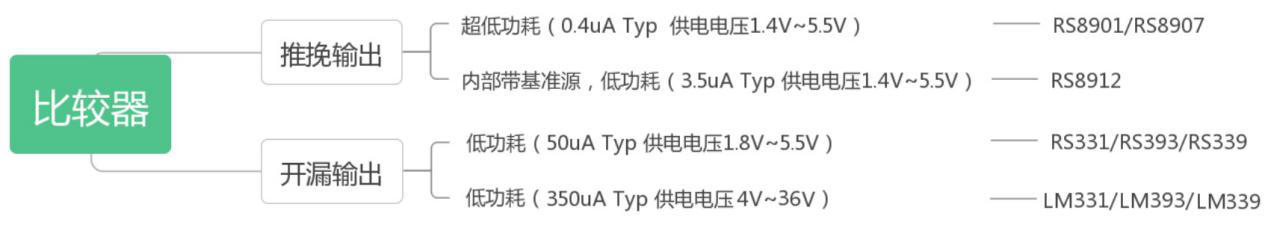

【2】润石科技比较器选型树状图