运算放大器-比较器基础知识解析

2022-06-23

2022-06-23运算放大器和比较器无论是外观还是原理图符号都差不多,如果把它上边的标识打磨掉的话很难区分开;二者在电子设计中都有着广泛而重要的应用,加之很多电路中会出现将运放用作比较器的应用,以至于有工程师朋友时不时的会将运算放大器和比较器两者混淆。

1、运放原理简介

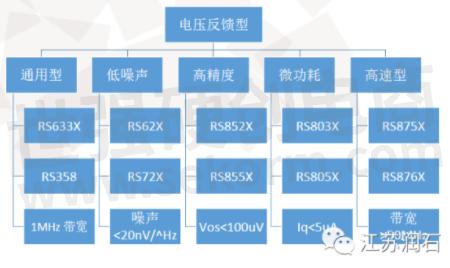

运算放大器,是一种用于信号调理的模拟芯片。比如对信号作放大,滤波,求和等。常见的有电压反馈型运放和电流反馈型运放。这里只介绍电压反馈型运放,继续细分可以分为下图所示。如果按照制造的工艺来区分,可以分为Bipolar(三极管)工艺,CMOS工艺,JFET工艺。目前的低压运放主要是以CMOS工艺为主,因为其有输入偏置电流小,综合性能优异等优势。从应用的角度来看,分为低压供电和高压供电,低压供电为5V以内,高压供电为5V以上,一般有24V耐压,36V耐压等级。

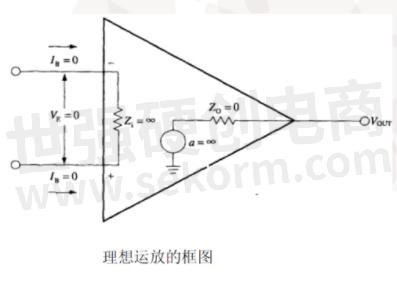

标准运放的符号如图所示,一个同相输入端,一个反相输入端,一个输出端,一个正电源引脚,一个负电源引脚。所以运放是差分输入,单端输出的(全差分运放除外)。运放本身并没有参考点,所以为了能够正常工作,外面的电路需要给运放一个稳定的参考点。

1、运放原理简介﹣-(续)

运放会放大其两个输入端的电压差,输出电压等于运放的开环增益乘以输入电压差,而运放自身的直流开环放大倍数至少有80dB(一万倍)以上,因此只要输入端电压有 uV 级别的压差,输出就会有很大的电压。当然这种开环放大在实际中是不好用的,因为运放的开环增益会随温度,负载,输入电压差大小而变化,为了得到稳定的放大倍数,在实际应用中都是引入负反馈来維持稳定的。

理想运放的特点:

①输入电阻无穷大

②输入失调电压为零

③输入偏置电流,失调电流为零

④开环增益无穷大

⑤输出阻抗为零

⑥带宽无穷大

⑦压援率无穷大

正是因为现实中不存在理想的运放。才会们衍生出来各式各样的的放大器,不同的应用关注的指标参数不一样,总是需要强化某个指标,而弱化某个指标,选一个折中的来设计运放。

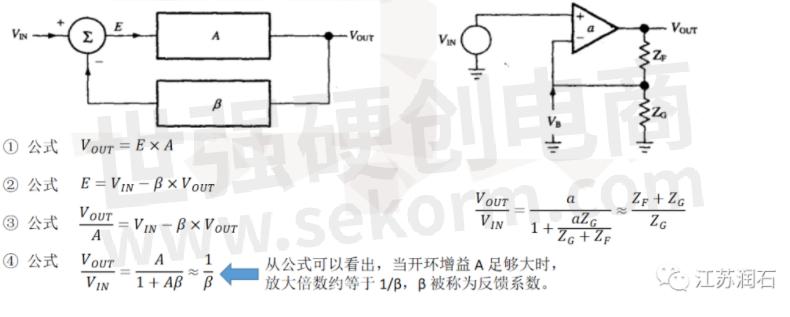

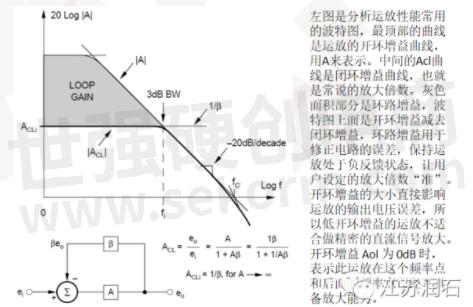

2、负反馈的本质

为了稳定的放大,需要引入负反馈。负反馈本质上是利用输出的一部分信号反馈到输入,用运放超高的开环增益来修正许多因素导致的误差。超高的开环增益迫使输入端的压差保持在 uV 级别,也就是运放输入端虛短。 CMOs 运放输入偏置电流极小,运放输入端虚断。

3、运放的主要参数:

①供电电压范围

②共模电压输入范围(Vcm)

③输入输出轨到轨特性(Rail to Rail Input/output)

④带宽增益积(GBW/GBP)

⑤压摆率(SR)

⑥建立时间(Settingtime)与过驱动恢复时间(Overload Recovery time)

⑦失调电压(Vos)与温漂(Vos/T)

⑧输入偏置电流(IB)与失调电流(Ios)

⑨噪声(Vnoise)

⑩开环增益(Aol)

⑪共模抑制比(CMRR)

⑫电源抑制比(PSRR)

⑬输入电容(Cin)

⑭静态电流(Iq)

⑮全谐波失真加噪声(THD+N)

⑯开环输出阻抗(Ro)与闭环输出阻抗(Rout)

⑰相位裕度(φm)

①供电电压范围

运放自身没有“地(GND)”的概念,标准运放只有两个电源引脚,正电源VCC和负电源VEE,因此运放的供电电压指的是VCC-VEE的差,习惯上把供电电压范围分为低压(6v以内),高压(6V以上)。常见的高压运放耐压等级一般有24V,36V。耐压等级是跟选取的制造工艺有关系的

运放有供电电压范围,意味着有最小值和最大值,供电电压需要大于最小值,才能让运放正常工作。供电电压不能超过最大值,否则运放内部会击穿。

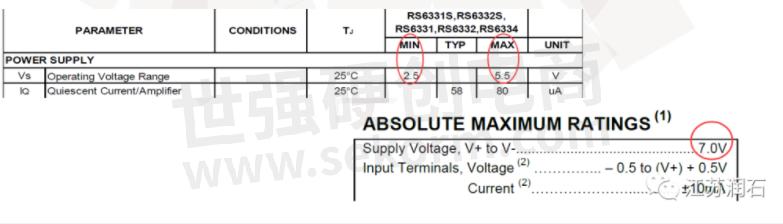

一般规格书会标明两个供电电压值,建议值和极限值。建议值是厂家考虑了制造工艺的离散性,预留一定的余量。如下是润石通用系列运放RS633X的规格书,建议值是2.5V~55V,实际上供电电压位于2.2V~2.5V运放都能工作,但是带窗,噪声,勒到勒输出能力等参数都会恶化,因此最好是位干25V以上工作。55V~7V区间也能正常工作,但是大危险了,供电电压稍有波动就可能烧掉运放,因此厂家的建议最大值是5.5V。

②共模电压输入范围(Vcm)

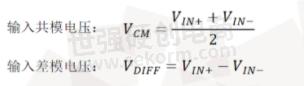

首先要理解什么是共模电压,什么是差模电压。对于运放的同相输入端(vin+)和反相输入端(Vin-)来说:

输入共模电压定义了一个允许的输入范围,超出这个范围后,会引起运放输入级对管的异常,此时运放将不能线性的工作。RS633X的输入共模电压范围如下表所示。

![]()

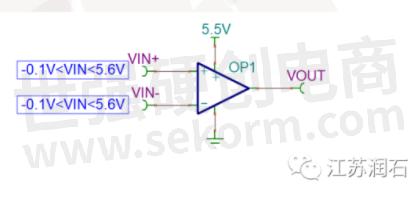

通俗来说,规格书里面给出的输入共模电压范围,还有输入差模电压范围,目的只有一个,就是保证加在 VIN+ 和 VIN-上的电压不能超过允许的电压范围。对于RS633X来说,输入电压的范围只允许在VSS-0.1V~VCC+0.1V之内,如果供电电压是5.5V,那么输入允许的电压范围就是-0.1V~5.6V。

③输入输出轨到轨特性(Rail to Rail Input/output)

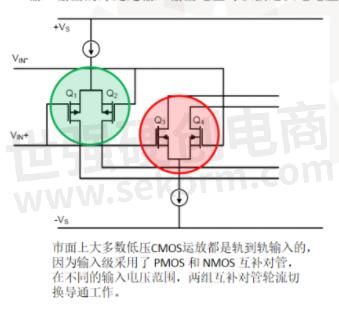

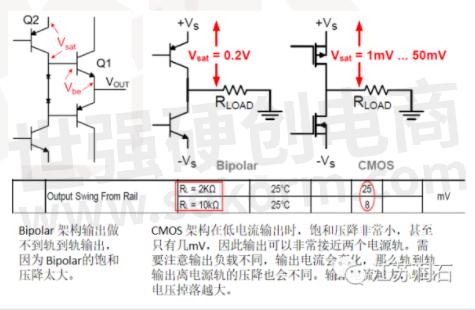

“轨”是指电源轨,包括正电源轨和负电源轨,如果负电源轨是接地,那么负轨就是地(GND),正轨就是VCC。传统的Bipolar(三极管)工艺JFET工艺,都做不到轨到轨输入。CMOS工艺在输入级用一对PMOS和一对NMOS组成互补输入,可以做到轨到轨输入。轨到轨输出是指输出端的电乐可以接近正轨和负轨,注意是接近,不是等于。轨到轨输入输出的好处是输入输出电压可以接近供电电压,这样在低供电电压时输入输出的动态范围可以做得最大化。

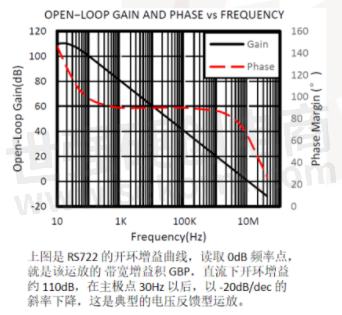

④带宽增益积(GBW/GBP)

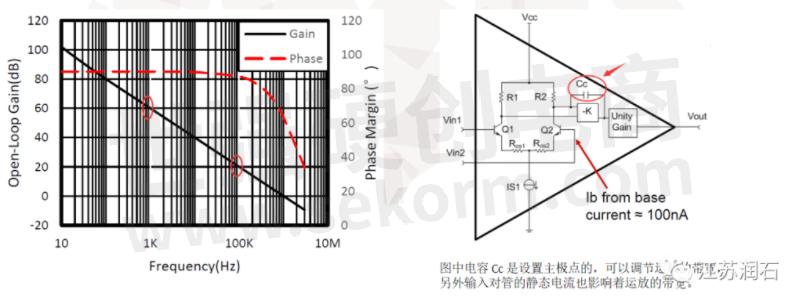

对于电压反馈型运放来说,有带宽增益积的概念,因为观察电压反馈型运放的开环增益曲线,从主极点以后,带宽和增益的乘积几乎是一个常数。对于电流反馈型运放来说,这个是不成立的。

通常用开环增益曲线与0 dB相交处为带宽增益积,(有时候高带宽的运放并不成立)。下图是RS633X的开环增益曲线,可以看到,0dB相交处,约为11MHz,表示该器件在单位增益同相放大时,带宽为11MHZ。

④带宽增益积(GBW/GBP)---(续)

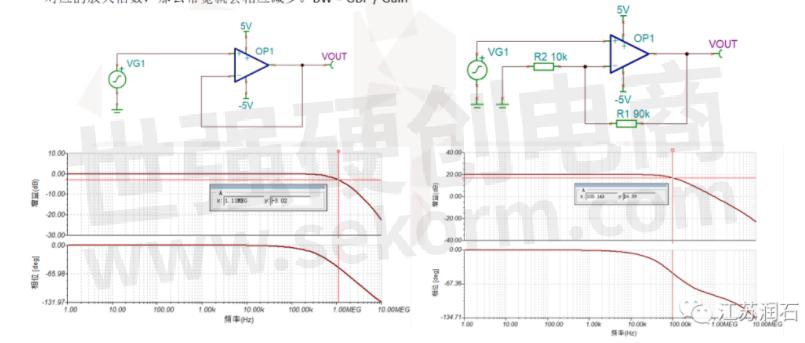

对于不同的增益(需要用噪声增益去计算),厂家规格书给出的带宽增益积一般都是单位增益时的带宽,如果电路有对应的放大倍数,那么带宽就会相应减少。BW=GBP/Gain

⑤压摆率(SR)

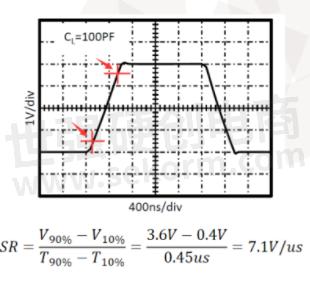

压摆率,Slew Rate,是描述运放对于大信号边沿响应的快慢。从下面的波形中可以看出具体的定义。输入共模电压大小,温度的高低,都会影响压摆率SR的大小。实际应用可用公式计算:SR=2πf*Vp

比如想在10kHz频率下,保持正常的输出幅度5Vp,那么SR=2*3.14*10000*5/1000000=0.314V/us。需要用0.314V/us以上压摆率的运放才可以。由此引申出运放另外一个带宽,全功率带宽(FullPower Bandwidth),运放的实际带宽由全功率带宽和小信号带宽中的最小值来决定。

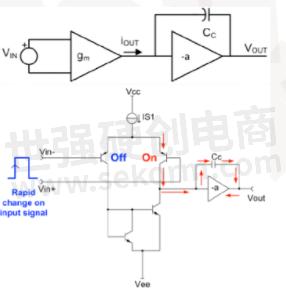

从运放内部看,对主极点电容Cc充放电的电流大小决定了压摆巡的值。在小信号输入时(通常100mVpp以内),充放电的电流跟输入信号的幅度是线性关系,此时输出信号上升和下降时间并不是用压摆率SR来计算的,此时运放的边沿上下时间近似一阶电路的响应计算

![]()

实际上比用压率 SR 来计算快得多。当输入信号为大信号时,充放电电流增大以至于被限制在最大值,类似于一个电容被恒流充电,那么电容的输出电压就是呈线性上升,此时上升下降时间要用压摆率 SR 来计算。

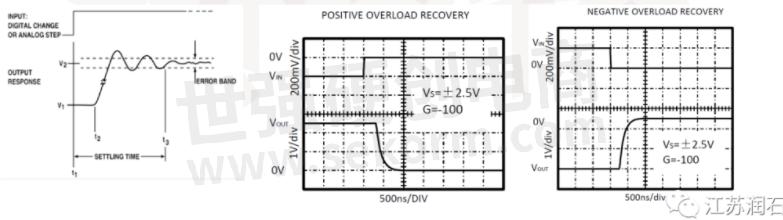

⑤建立时间(Setting time)与过驱动恢复时间(Overload Recovery time)

建立时间,是运放的阶跃响应输出稳定到一定精度所需要的时间。由于受到运放小信号带宽和压摆率的限制,运放的阶跃响应总是需要一定的时间,而且随着相位裕度不同,输出电压的波动也有很大差异。

对于小信号输入(通常100mVpp以内),输出电压的上升时间是Trise=0.35/f,然后再加上后段稳定到需要精度的时间,就构成了小信号输入时的建立时间。对于大信号输入,输出电压上升的时间用压摆率计算,大信号输出时一般没有过冲振铃,因此整个上升时间构成了建立时间。建立时间主要受运放主极点电容Cc充放电的值和相位裕度影响。

过驱动恢复时间,是指放大后的输出电压超过了电源的供电电压,当输入信号跳变时,输出电压延迟的响应时间。该参数是受运放内部的输出级影响,主要是输出管退出饱和状态的时间。

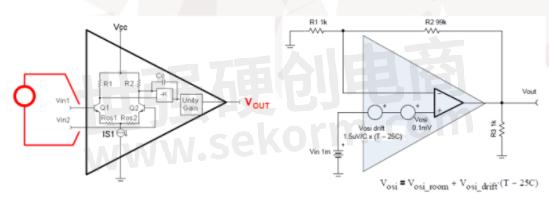

⑦失调电压(Vos)与温漂(ΔVos/AT)

理想运放输入电压为零时,输出电压也为零。实际上由于工艺的限制,运放的输入级做不到完全对称,输入失调电压 Vos,是指为了让运放的输出为零,需要额外在输入端补偿的电压值。

CMOS运放的失调电压在5mV~10mV,出厂时可以经过品员级的激光修调(Trim),失调电压可以收窄到最大0.5mV,而封装后的电子修调,可以精确到50uV级别,如果需要更加小的失调电压,运放需要用自稳零技术,斩波和自稳零技术可以把失调电压控制在1uV级别。失调电压在某个范围时是有一定的条件的,比如规格书一般都是在共模电压为一半VCC时测试的。实际应用中,比如VCC=5V时,当共模电压在0V~3.7V时,输入PMOS对管工作,失调电压较小。当共模电压在3.7V~5V时,输入NMOS对管工作,NMOS对管一般不进行修调,此时失调电压较大,达不到规格书的标称值。

温漂是指运放的失调电压会随温度的变化而发生变化,Bipolar(三极管)工艺的运放温漂比较线性单调,CMOS工艺的运放温漂不是线性单调的,但是为了方便描述,统一归一化为X mV/℃。

运放的失调电压和温漂会被线性放大, 左图中,运放的失调电压Vos=0.1mV,温漂为1.5uV/℃,电路配置放大100倍。

Vout

=(Vos+Vdirft X(T-25℃)x100

失调电压通常拥有正态分布的特性, 正常应用时一般取最大值计算。为了减少 失调电压和温漂带来的误美。作直流放大时,通常取最低输入信号的十分之一来保持输出电压的精度。当然,如果电路是作交流放大,那么失调电压不会被放大,对输出影响有限。

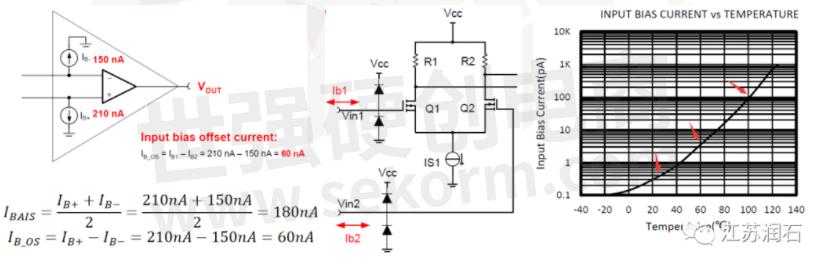

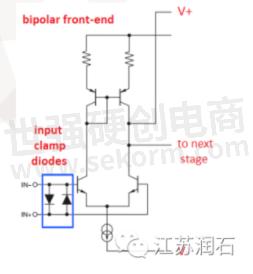

⑧输入偏置电流(Ir)与失调电流(los)

理想运放的输入偏置电流和失调电流为零,早期使用Bipolar(三极管)工艺时,由于三极管属于电流控制型元件,运放的两个输入端是三极管的基极,因此有偏置电流。CMOS属于电压控制型元件,其极电流为pA级别,基本上可以忽略不计。CMOS运放输入偏置电流和失调电流受温度变化影响较大,常温下几乎为零,随着温度的上升,输入偏置电流和失调电流指数增大,这是因为CMOS运放输入引脚的ESD保护二极管漏电引起的,除非选用特别的制造工艺,否则超过100温度下,输入偏置电流都会增大成百上千倍。在一些高输出内阻的传感器信号放大中,可能会引起额外问题,如果放大电路外部使用的电阻是百kΩ级别,那么在运放输出端将会产生新的失调误差。

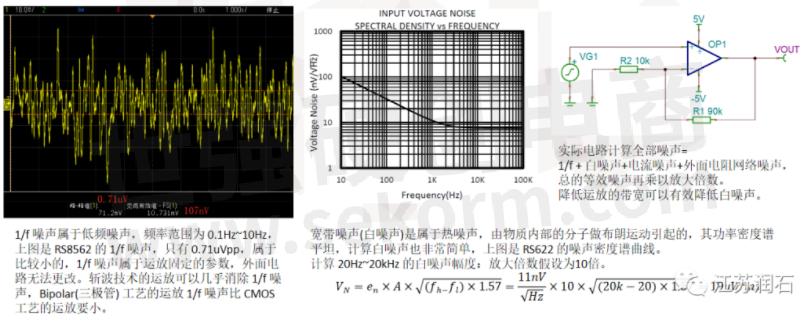

⑨噪声(Vnoise)

三极管,MOS管,电阻,都会产生噪声。在运放中,噪声主要有两种,低频噪声(1/f),宽带噪声(白噪声)。在通用架构的运放中,存在电压噪声和电流噪声,噪声由于是一个随机的信号,为了方便描述,用其功率密度谱来衡量,这样方便画出噪声功率密度谱与频率的关系,最直观的方式就是用Vpp值或者Vrms值描述,一般Vpp=6.6*Vrms。

⑩开环增益(Aol)

运放的开环增益就是不加负反馈时的频率响应特性。运放直流的开环增益高达100dB(十万倍)以上,如此高的开环增益,在实际上是不适合直接放大信号的,开环增益直接受温度、输出负载,供电电压输入电压幅度影响,而目会大幅度的波动,所以一定需要引入负反馈来提高闭环增益的稳定性,单独对比直流下的开环增益意义不大。

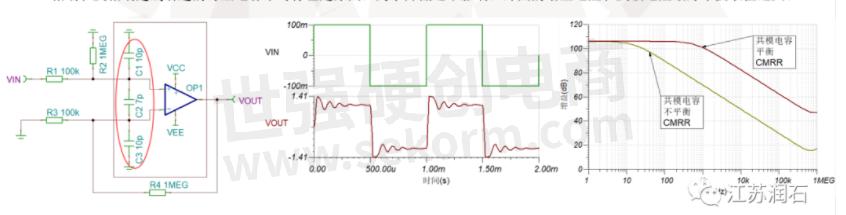

⑪共模抑制比(CMRR)

理想情况下,运放只会放大其两个输入端的电压差,对于共模电压完全不响应。共模抑制比描述的是运放对输入的共模电压的抑制能力,输出端以失调电压的误差形式表达,一种简单的测量方式是在输入端加一个固定的共模电压,测量运放输出的偏移量,来计算共模抑制比。

实际运放对共模信号无法完全抑制,是由于运放输入对管在工艺上没办法做到完全对称,包括输入对管的跨导增益,寄生电容,温度系数等。而且共模抑制比是频率的函数,频率越高,共模抑制比越低。

为了提高差分放大电路的共模抑制比,就要求左图四个电的匹配度要非常高,如果电阻的精度是1%,那么直流下的共模抑制比只有46dB。为了解决这个问题,芯片厂家专门生产了包含四个高精度电阻的差分运放,这样直流下的共模抑制比可以高达100dB。在电路设计上,同相放大器电路,两个输入端的电压跟随输入信号,会由于其模抑制比的原因而在输出端产生额外失调电压。对于高精度的ADC采样,可能会影响后几bit读数。反相放大器电路,其同相端一般接到古定的参考电压上,运放两个输入端的电压比较恒定,因此在输出端产生的失调电压相对较低。

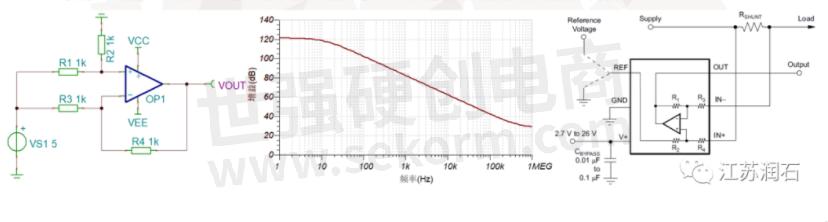

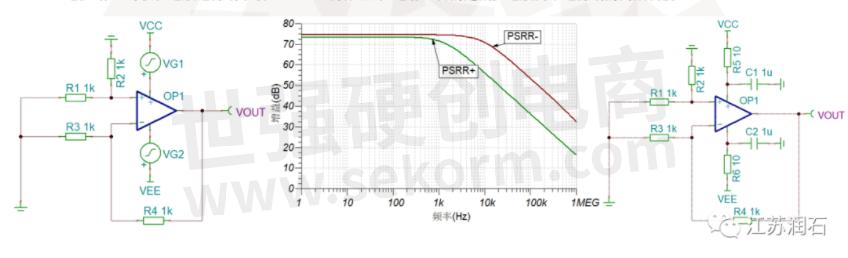

⑫电源抑制比(PSRR)

运放的电源电压波动时,会轻微影响内部的恒流源静态点,导致运放输出端以失调电压的形式出现误差。电源抑制比描述的是运放对电源波动的抑制能力,通常分为对正电源轨PSRR+,负电源轨PSRR-的抑制能力,两者通常有点差异。电源抑制比也是频率的函数,频率越高,电源抑制比PSRR越低。

电源抑制比的测量如左图所示,通过测量运放输出端的残余信号来计算。从右图PSRR曲线可以看出,低频下都有很好的抑制能力,当频率逐渐升高时,开始以-20dB/dec下降,这是因为运放内部差分对的拖尾恒流源的电容随频率改变,恒流源的等效阻抗随频率升高而减少。所以如果应用中的负电源VEE由DC-DC或者电荷泵等器件产生,那么需要做好滤波工作,可以在运放电源端串联RC,LC,或者磁珠+电容,目的是减少运放两个电源端的高频纹波。

⑬输入电容(Cin)

运放的输入电容分为共模输入电容和差模输入电容,现在的CMOS运放大多数具有EMI抑制功能,其共模输入电容和差模输入电容会偏大一点,大概有10pF~20pF。运放的输入电容在某些应用下会引起问题,主要有引起输出振荡,或者由于两个输入端的共模电容偏差较大,引起共模抑制比恶化。

反相端的输入共模电容会与反馈电阻RF形成一个极点,从输出端反馈回来的信号会有相移,再回馈到反相端,造成同相端和反相端的相移不是正常的对应状态,输出电压会存在过冲或者直接振荡。要解决此问题,一个是需要等比例整体降低反馈电阻的阻值,另一个是在反馈电RF上并联电容,引入额外的零点来修正造成的相移。

共模输入电容如果不对称平衡,会引起共模抑制比的恶化,因为运放同相端和反相端的相移不相等,自然进入运放的信号就不是对称的,此时共模信号也会被放大。除了运放自身引脚以及内部电路引起的不平衡以外,PCB Layout时,同相端和反相端走线引起的寄生电容不对称也是原因,为了降低这个影响,外围的增益电阻和反馈电阻最好不要取值过大。

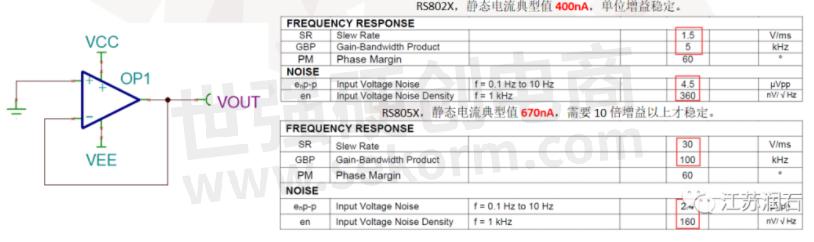

⑭静态电流(Iq)

运放的静态申流是指运放外干放大状态,并目其输入共模电压外干某个电压,器件自身消耗的电流,输出负载的电流是不计算在内的。因为标准的运放没有接地引脚,所以流入VCC引脚的电流约等于流出VEE引脚的电流。运放生产商测试运放的静态电流时,采用下冬的电路,正负电源供电,配置成缓冲器,同相端接地,相当于输入共模电压是运放供电电压的一半,然后测试vcC和VEE引脚的电流,输出引脚不能接入负载。

运放的静态电流是内部众多恒流源偏置电流的来源,包括输入差分对管,输出推挽对管等。静态电流直接影响运放众多的参数,比如带,噪声,压摆率等。静态申流越大,带宽和压摆率越高,噪声更低。所以高速(GBP>100MHz)的运放其静态电流一般都是5mA/ch以上。对干现在很多10T设备的应用,又希望静态电流做的非常低,那么只能牺牲带宽,用摆率,噪声,相位裕度等指标,降低内部恒流源的偏置电流,来降低运放整体的静态电流。

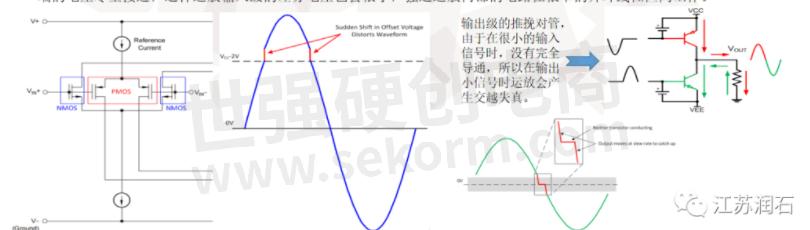

⑮全谐波失真加噪声(THD+N)

全谐波失真加噪声,计算公式为![]() 意思是一个信号经过运放后,统计其输出端各次谐波失真幅度,再加上带内噪声,最后得出一个有效值电压,相对于基波信号的比值。

意思是一个信号经过运放后,统计其输出端各次谐波失真幅度,再加上带内噪声,最后得出一个有效值电压,相对于基波信号的比值。

在音频领域应用中,THD+N非常重要,因为数字音频存储用的位数一般为24bit或者32bit,稍有些许失真就能把后面的几bit淹没掉,不过人耳对于一个信号的失真,大概5%以上的失真才可能听得出来。

一个信号经过运放后产生失真的原因,分为输入差分对管的交越失真,输入阻抗非线性,密勒电容电流的非线性,输出推挽级的交越失直。其中运放的负反馈会尽最大能力去修正以上的失直,负反馈最大的作用,就是让运放两个输入端的电压尽量接近,这样运放输入级的差分电压也会很小,强迫运放内部的电路在很窄的开环线性区间工作。

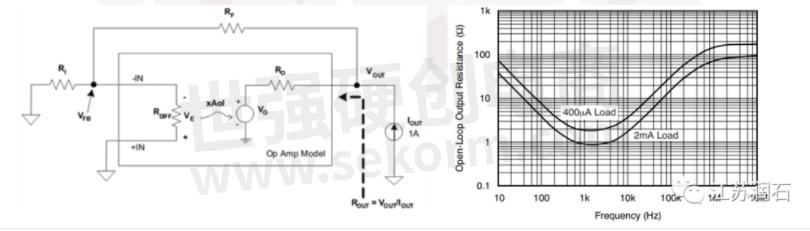

⑯开环输出阻抗(Ro)与闭环输出阻抗(Rout)

开环输出阻抗Ro是运放固有的特性,不随运放的增益而改变。闭环输出阻抗Rout相当于把整个运放的电路看成一个黑匣子,计算的是运放处于负反馈状态下输出端的阻抗。计算公式为![]() 。

。

Bipolar(三极管)工艺的运放开环输出阳抗比较平,到高频段才非线性。CMOS工艺的运放开环输出阳抗则复杂得多。没办法用固定的曲线来衡量,不同带宽,静态电流的运放开环输出阻抗差异很大。而且即使是同一个运放,输出负载吸取的直流电流不一样,开环输出阴抗也不一样,庆幸的是,运放的负反馈会帮我们解决这些问题。

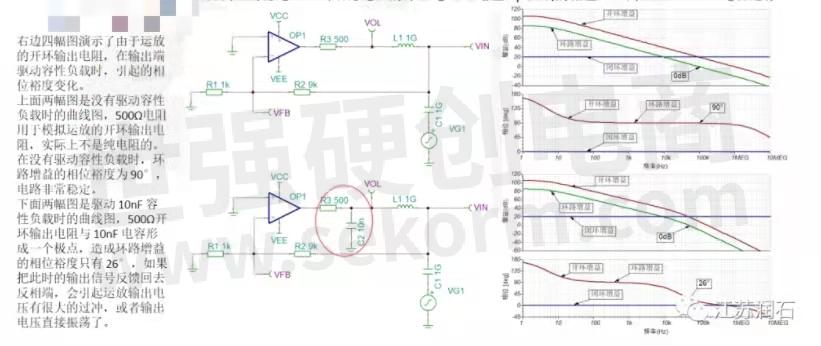

运放的开环输出阻抗最大的危害,就是如果运放输出端存在容性价截,那么一老就会在开环曲线上形成一个极占,如果极点在有用的频带内,相移会比较大,经过反相端反馈回来后,会造成运放振荡。所以CMOS工艺的运放,其输出端不要轻易直接用电容接地滤波,即使要对输出电压滤波,也要先串联一个电阻才能接电容到地。

⑰相位裕度(φm)

首先要了解运放处于负反馈状态下,增益跟频率的三条曲线,开环增益Aol,闭环增益1/β,环路增益Aol*β,简写Aβ。因为这三条曲线决定了运放负反馈的稳定性,判断稳定性的标准是环路增益AB曲线的相位,距离相移180°,是否还存在45°的相位裕度。

4、运放应用的问题探讨

a)运放最大能够放大多少倍?

b)运放可以放大多微弱的信号?

c)双电源供电的运放是否可以改成单电源供电?是否可以不对称供电?

d)运放的输出总误差是什么?

4、运放应用的问题探讨---(续)

a)运放最大能够放大多少倍?

根据开环增益的曲线以及增益带宽积GBP的定义,Gain=GBP/Bandwidth,因此最大能够放大多少倍是跟带宽相关的,极限情况下放大超低频信号(比如0.1Hz),那么放大倍数可以接近Aol 曲线低频段增益,但是由于没有足够环路增益用于修正误差,此时输出电压将偏离理想的输出电压值,而目单级过高的放大倍数会把运放的失调电压。噪声放大,使电路“不好用”。建议单级放大电路控制在100倍以内。

b)运放可以放大多微弱的信号?

取决于所用运放的底噪水平。如果需要运放放大微弱信号(1uV~10mV),首先要让运放的输入共模电压远离两个电源轨,保证能够线性放大然后限制运放的带宽,这样能有效降低带外噪声。总之,只要有用信号不被噪声淹没,那么都能有效放大。

c)双电源供电的运放是否可以改成单电源供电?是否可以不对称供电?

可以,标准运放并没有地GND引脚,所以运放并不知道“地GND”在哪里,运放内部的电路都是参考VEE引脚的,但是对于输入的信号来说,因为运放放大的是输入的差分电压,因此必然会有输入信号的参考点,外理好输入共模电压的范围即可,负反馈的存在可以不对称供电。

d)运放的输出总误差是什么?

总共有9项误差构成, Verror=Vos+Vos_drift+Vbias+Vbias_drift+Vnoise +VCMRR+VPSRR+VAOI+VEMIRR

不管是直流放大还是交流放大,实际的输出电压跟理想的输出电压值之间的差距。就是以上9项误差构成的,而目运放的这些误差项。都是在一直变化的,随温度变,随时间变。引入负反馈非常重要,能够无时无刻地修正以上误差,当然不是“消除”,而是尽量减少。

5、运放与比较器的区别

运放的设计目的是用于存在负反馈的场合,比较器是用于开环应用。

a)为了负反馈稳定,运放内部有密勒电容,比较器则不需要,因此比较器没有压摆率这个参数。输入一个阶跃信号时,运放上升是慢吞吞的。而比较器则马上就翻转了。

b)一些高压的运放,还有Bioolar(三极管)工艺的运放,两个输入引脚之间会存在双向钳位二极管。低压的CMOS运放一般没有,比较器没有双向钳位的二极管。所以把运放当比较器来用,要判断是否需要加限流电阻,以免烧掉运放。

c)运放有带宽,比较器一般不用带宽来衡量其翻转速度,用TPHL,TPLH,Tfall,Trise,来表示速度。

一个简单的计算比较器速度方法是

d)运放输出端都是推挽输出的,比较器可以做成推挽输出,也可以做成开漏输出。

e)运放输出过载后,需要比较长的恢复时间。比较器的过载恢复时间非常短。

f)有些运放的输入共模电压范围,不能到正电源轨。许多比较器是支持到正电源轨的。

g)运放可以当比较器使用(在一些低速翻转场合可以),而比较器不能当运放使用。

6、如何根据应用选择合适运放

运放选择判断步骤:

1、实际工作电压,选用低压运放还是高压运放,高压运放比低压运放贵很多:

2、是否需要轨到轨输入/输出特性:

3、客户具体的应用场合,比如:

1)音频应用,注重带宽,压摆率,噪声,输出轨到轨特性

2)便携式产品应用,注重静态电流,带宽等:

3)传感器应用,注重失调电压,温漂,静态电流,输入偏置电流,共模抑制比等;

4)采样电流应用,注重带宽,失调电压,温漂,静态电流等:

5)滤波器应用,注重带宽,乐摆率,轨到轨输入输出特性等:

6)仪器仪表应用,注重失调电压,温漂,1/f噪声等:

7)医疗应用,注重噪声,带宽,轨到轨输入输出特性等。

7、润石公司运放和比较器的优势

运放:

全系列运放种类齐全,低噪声,高精度,高速,微功耗,通用型

有1μA/ch的微功耗运放,适合用于PIR,气体传感器等应用场合

通用系列运放有失调电压最大为0.5mV的版本

精密运放失调电压最大为5μV,温漂最大50nV/℃,比同行最大20nV要好

高压通用型运放,高压高精度型运放,高压差分运放,仪表放大器 即将发布。

比较器:

全系列比较器种类齐全,微功耗,通用型,高速型

有1μA/ch的微功耗比较器,适用于智能家居等超低功耗产品

RS331/RS393/RS339,通用型1路/2路/4路比较器,支持轨到轨输入进行比较。